Document Number: 0042SP0001-1009 Revision: 0.2.0 10/2009

# AK3671(B) Mobile Multimedia Application Processor

## Specification

(applicable to AK3671 and AK3671B)

© 2009 Anyka Technologies Corporation All rights reserved.

## **Table Of Contents**

| 1 | Int | trodu | uction                               | 1  |

|---|-----|-------|--------------------------------------|----|

|   | 1.1 | С     | onventions                           | 2  |

|   | 1.2 | Fe    | eatures                              | 3  |

|   | 1.3 | Та    | arget Applications                   | 4  |

|   | 1.4 | Pı    | roduct Documentation                 | 4  |

|   | 1.5 | 0     | rdering Information                  | 4  |

| 2 | Si  |       | s and Connections                    | 5  |

|   | 2.1 | Pi    | in Definitions                       | 5  |

|   | 2.2 | SI    | hared-Pin List 1                     | 2  |

| 3 | Fu  |       | onal Description1                    |    |

|   | 3.1 | PI    | MU 1                                 |    |

|   | 3.′ | 1.1   | LDO and DC/DC Regulator 1            |    |

|   | 3.1 | 1.2   | Typical Power-On Time 1              | 7  |

|   | 3.1 | 1.3   | Temperature Detector                 |    |

|   | 3.2 | S     | ystem Control 1                      |    |

|   | 3.2 | 2.1   | Clock Generation and Control 1       |    |

|   | 3.2 | 2.2   | Reset Module                         |    |

|   | 3.2 | 2.3   | Interrupt Module                     |    |

|   | 3.2 | 2.4   | Bootstrap Module2                    | 2  |

|   | 3.2 | 2.5   | Power Management                     | 2  |

|   | 3.2 | 2.6   | Working Modes                        |    |

|   | 3.2 | 2.7   | JTAG                                 | 2  |

|   | 3.3 |       | TC Module                            |    |

|   | 3.4 | С     | PU core                              | :3 |

|   | 3.5 | М     | emory                                | 24 |

|   | 3.5 | 5.1   | On Chip Memory2                      | 24 |

|   | 3.5 | 5.2   | External Memory2                     | 24 |

|   |     | 3.5.2 | 2.1 RAM Interface                    | 24 |

|   |     | 3.5.2 | 2.2 Nand Flash Interface 2           | :6 |

|   | 3.6 | A     | dvanced High-performance Bus (AHB) 2 | 27 |

|   | 3.7 | D     | MA/CRC Accelerator                   | 27 |

| 3.8  | Register Bus Controller |                                       |  |  |  |  |  |

|------|-------------------------|---------------------------------------|--|--|--|--|--|

| 3.9  | Video Processor         |                                       |  |  |  |  |  |

| 3.9  | .1 Typical Encodi       | ng Application                        |  |  |  |  |  |

| 3.9  | .2 Typical Decodi       | ng Application29                      |  |  |  |  |  |

| 3.10 | Image Processor         |                                       |  |  |  |  |  |

| 3.1  | 0.1 Typical Encodi      | ng Application                        |  |  |  |  |  |

| 3.1  | 0.2 Typical Decodi      | ng Application                        |  |  |  |  |  |

| 3.11 | Audio Processor         |                                       |  |  |  |  |  |

| 3.1  |                         | ng Application                        |  |  |  |  |  |

|      |                         | ng Application                        |  |  |  |  |  |

| 3.12 | I2S Interface           |                                       |  |  |  |  |  |

| 3.1  | 2.1 Timing              |                                       |  |  |  |  |  |

| 3.1  | 2.2 Typical Applica     | tions                                 |  |  |  |  |  |

| 3    |                         | r modes                               |  |  |  |  |  |

| 3    |                         | lode                                  |  |  |  |  |  |

| 3.13 | Software I2C            |                                       |  |  |  |  |  |

| 3.14 |                         |                                       |  |  |  |  |  |

| 3.1  |                         |                                       |  |  |  |  |  |

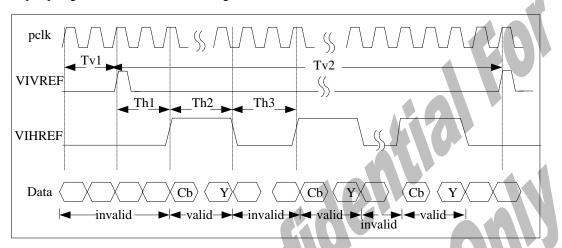

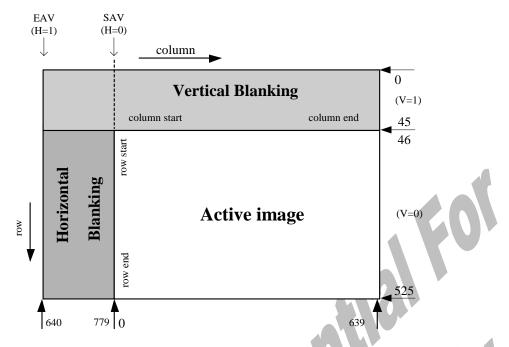

| 3    | 3.14.1.1 External In    | hage Sensors Compatible With CCIR 601 |  |  |  |  |  |

| 3    | 3.14.1.2 External In    | hage Sensors Compatible With CCIR 656 |  |  |  |  |  |

| 3.1  | 4.2 Typical Applica     | tion 40                               |  |  |  |  |  |

| 3.15 | LCD Controller          |                                       |  |  |  |  |  |

| 3.1  | 5.1 Working Modes       |                                       |  |  |  |  |  |

|      | 5.2 Timing and Dat      | a format                              |  |  |  |  |  |

| 3    | 3.15.2.1 MPU Inter      | ace                                   |  |  |  |  |  |

|      | 3.15.2.1.1 16-bit M     | IPU Interface                         |  |  |  |  |  |

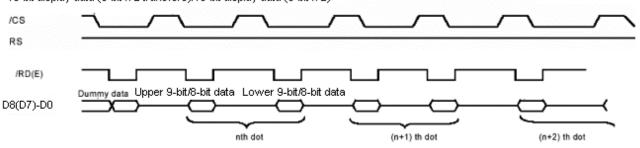

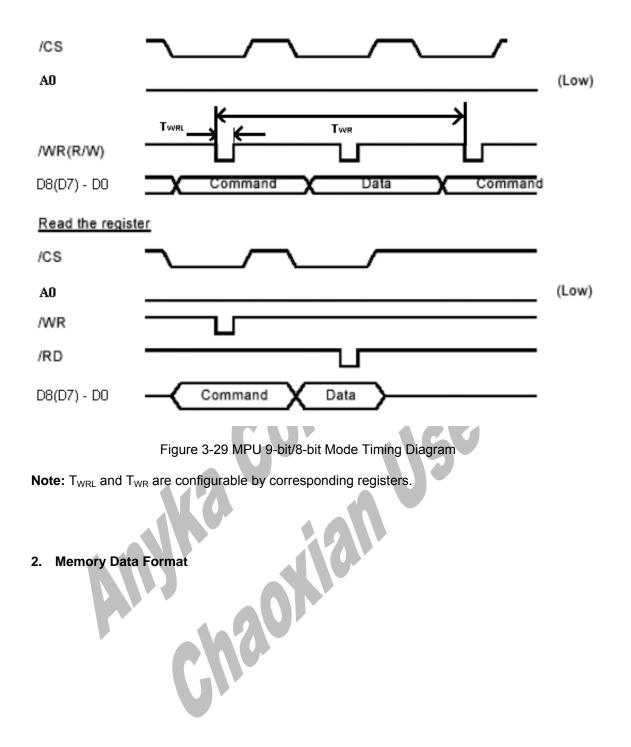

|      | 3.15.2.1.2 9-Bit/8-     | bit MPU Interface                     |  |  |  |  |  |

| 3.1  | 5.3 Black-and-Whit      | e Panels and Gray-Scale Panels 49     |  |  |  |  |  |

| 3.16 | UART                    |                                       |  |  |  |  |  |

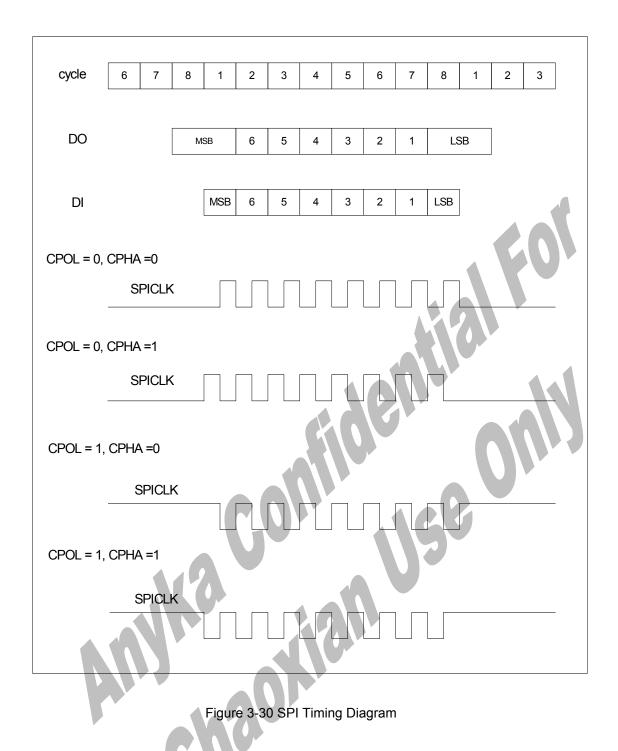

| 3.17 | SPI                     |                                       |  |  |  |  |  |

| 3.18 | USB 2.0 HS Device       |                                       |  |  |  |  |  |

| 3.19 | MMC/SD Interface.       |                                       |  |  |  |  |  |

| 3.20 | Audio Analog Comp       | onents 59                             |  |  |  |  |  |

|      |                         |                                       |  |  |  |  |  |

Publication Release Date: October, 2009

| 3.20   | 0.1 A   | ADCs                           | 59         |

|--------|---------|--------------------------------|------------|

| 3      | .20.1.  | 1 Reference Voltage Generator6 | 51         |

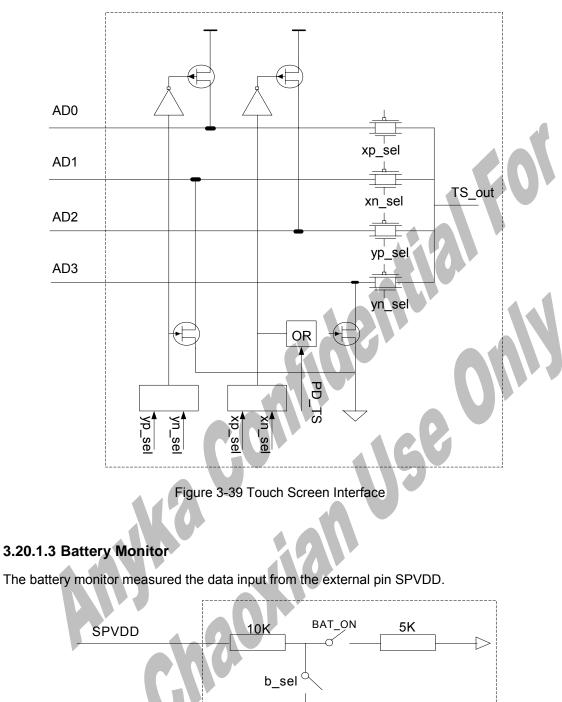

| 3      | .20.1.2 | 2 Touch Screen Interface6      | 51         |

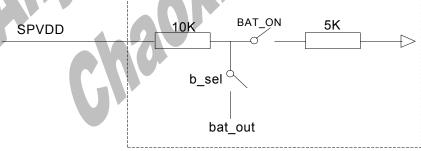

| 3      | .20.1.3 | 3 Battery Monitor6             | 32         |

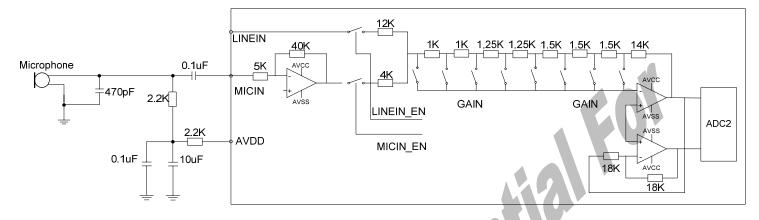

| 3      | .20.1.4 | 4 Microphone Interface6        | 33         |

| 3.20   | 0.2 [   | DACs6                          | 33         |

| 3.20   | 0.3 L   | ine In Interface               | 34         |

| 3.21   | PWN     | ۱                              | 35         |

| 3.22   | Time    | rs6                            | 35         |

| 3.23   |         | Σε                             |            |

| 4 Elec | ctrical | Specifications                 | 37         |

| 4.1    |         | mum Ratings6                   |            |

| 4.2    | Reco    | mmended Operating Range6       | 37         |

| 4.3    |         | electrical Characteristics     |            |

| 4.4    |         | lectrical Characteristics      |            |

| 5 PIN  |         | and Package Information        |            |

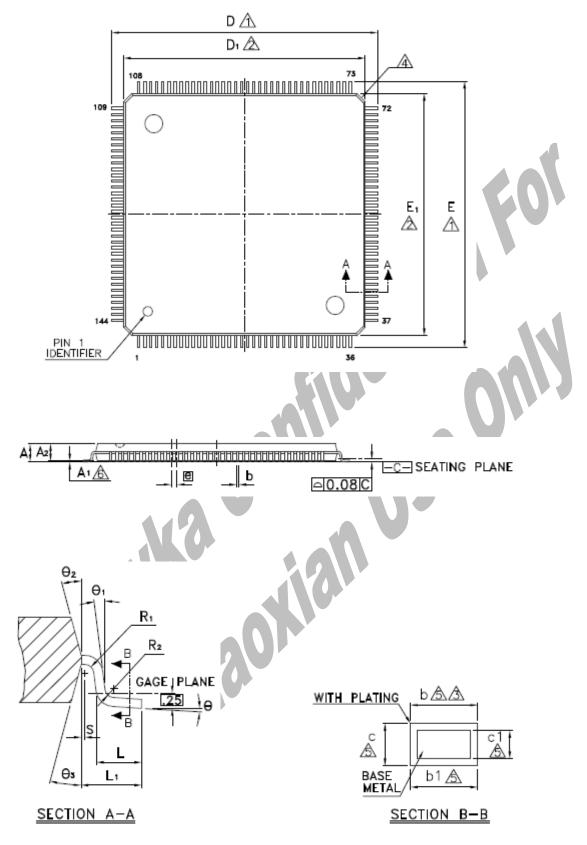

| 5.1    | AK36    | 571                            | <b>'</b> 0 |

| 5.1.   | .1 F    | Pin Assignment                 | <b>'</b> 0 |

| 5.1.   |         | Package Information            |            |

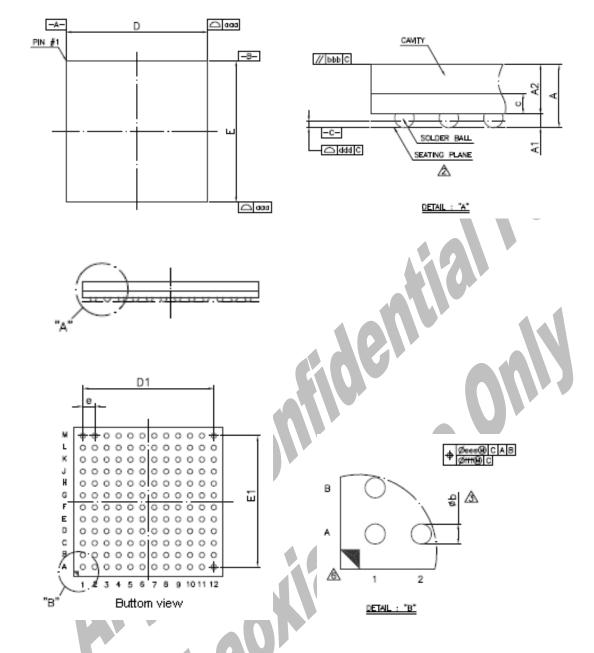

| 5.2    | AK36    | 571B                           | '5         |

| 5.2.   |         | Pin Assignment7                |            |

| 5.2.   | .2 F    | Package Information            | '6         |

|        |         | Jackage Information            |            |

Revision: 0.2.0

The copyright reserved by Anyka Technologies Corporation. Reproduction or distribution of this document and its content is prohibited without written confirmation of Anyka.

All intellectual property right relating to this document and its content reserved by Anyka Technologies Corporation or legally authorized by its partners.

THE INFORMATION IS PROVIDED WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WITHOUT LIMITATION WARRANTIES OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY OF ANY THIRD PARTY RELATING TO ANYKA PRODUCTS. IN NO EVENT SHALL ANYKA BE LIABLE FOR ANY DAMAGES WHATSOEVER ARISING OUT OF THE USE OR EXECUTION OF THIS DOCUMENT AND ITS CONTENT

This document provides the information "AS IS". Anyka may make changes to this document, or to specifications, product descriptions, and plans described therein at any time, without notice.

## **Contact Information**

Shenzhen Anyka Microelectronics Technology Co., Ltd. Room 203, Building 14, Shenzhen Software Park, Nanshan Branch, Nanshan District,

Shenzhen, Guangdong 518057

P. R. China

Tel: (86)755-8631 9669

Fax: (86)755-8615 3098

Anyka (Guangzhou) Microelectronics Technology Co., Ltd.

E-mail:

sales@anyka.com

Shenzhen Anyka Microelectronics Technology Co., Ltd., Beijing Office Room 2-1007, No. 1 Shanyuan Street, Zhongguancun,Haidian District, Beijing 100088 P. R. China Tel: (86) 10-8277 4086 Fax: (86) 10-8277 4086

Home Page: http://www.anyka.com

## **Document Revision History**

The following table provides revision history for this release. This history includes technical content revisions only and not stylistic or grammatical changes.

| VERSION | DESCRIPTION                                                                                                                                                                                                                       | DATE<br>COMPLETED   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 0.1.0   | Initial release                                                                                                                                                                                                                   | October, 2009       |

| 0.2.0   | <ol> <li>Section 3.20.1.4 &amp; Section 3.20.3:<br/>Modified Figure 3-41 Microphone Interface Architecture ar<br/>Figure 3-44 Line in Interface.</li> <li>Section 5.2.2:<br/>Added the package information of AK3671B.</li> </ol> | nd<br>October, 2009 |

## About This Manual

This document is the electrical and mechanical specification data sheet for the AK3671 and AK3671B processors. This specification contains a functional overview, mechanical data, package signal locations, electrical specifications (simulated), and bus functional waveforms.

\_ations (

## Definitions, Acronyms, and Abbreviations

Unless otherwise specified, all the acronyms and abbreviations used in this manual are defined hereunder.

| ADC  | Analog to Digital Converter                                                         |

|------|-------------------------------------------------------------------------------------|

| AHB  | Advanced High-performance Bus                                                       |

| ASIC | Application-Specific Integrated Circuit, refers to all the functional blocks of the |

|      | processor                                                                           |

| CMOS | Complimentary Metal-Oxide Semiconductor                                             |

| CRC  | Cyclic Redundancy Check                                                             |

| DAC  | Digital to Analog Converter                                                         |

| DMA  | Direct Memory Access                                                                |

| ECC  | Error Correction Code                                                               |

| FIFO | First In First Out                                                                  |

| GPIO | General Purpose Input/Output                                                        |

| I2C  | Inter-Integrated Circuit                                                            |

| I2S  | Inter-IC Sound                                                                      |

| JPEG | Joint Picture Expert Group                                                          |

| JTAG | Joint Test Action Group                                                             |

| LCD  | Liquid Crystal Display                                                              |

| LSB  | Least Significant Bit                                                               |

| MMC  | Multimedia Card                                                                     |

| MMU  | Memory Management Unit                                                              |

| MPEG | Moving Picture Experts Group                                                        |

| MSB  | Most Significant Bit                                                                |

| PMU  | Power Management Unit                                                               |

| PGA  | Programmable Gain Amplifier                                                         |

| PWM  | Pulse-Width Modulator                                                               |

| PLL  | Phase Locked Loop                                                                   |

| QFP  | Qual Flat Package                                                                   |

| RAM  | Random Access Memory                                                                |

| ROM  | Read Only Memory                                                                    |

|      |                                                                                     |

- RTC Real Time Clock

- SD Secure Digital

- SDRAM Synchronous Dynamic Random Access Memory

- SPI Serial Peripheral Interface

- UART Universal Asynchronous Receiver/Transmitter

- USB Universal Serial Bus

- XTAL

## **1** Introduction

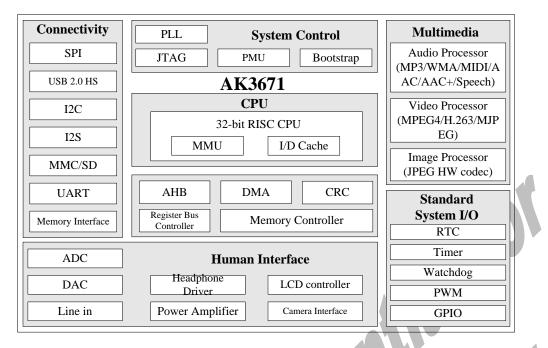

As new members of AK36XX series mobile multimedia application processors, AK3671(B) application processors are designed specially to bring industry-leading multimedia performance and high system integration for digital products. Compared with their compeers, AK3671(B) integrates more functional blocks, such as LDOs, camera interface, video encoders, etc., and enhances the performance, such as PMU efficiency.

AK3671(B) features the advanced and power-efficient 32-bit microprocessor core. Integrated with a powerful video decoder, a high-performance audio decoder, an image processor, a 10-bit SAR ADC, a 16-bit sigma-delta ADC, two 18-bit Sigma-Delta DACs, a power amplifier, a headphone driver, a USB 2.0 HS Device controller, a Multimedia Card/Secure Digital Host Controller (MMC/SD), and Power Management Unit (PMU), AK3671(B) offers a suite of peripherals to enable any product to provide rich multimedia experience at low cost and in small dimension. In addition, the AK3671(B) application processors are packaged in QFP, which is convenient and handy for the manufacturing and maintenance of final devices.

For cost-sensitive applications, the Nand Flash controller allows low-cost Nand Flash devices to be used as main non-volatile storage, on which the boot code can be saved. And the on-chip ECC circuitry of Nand Flash controller improves the reliability of data and code.

Unless otherwise specified, this specification is applicable to AK3671 and AK3671B. It should be noted that AK3671 and AK3671B are the same with the exception of their packages: AK3671 (QFP package) and AK3671B (BGA package). In the following sections only the AK3671 is described.

Figure 1-1. AK3671 Functional Block Diagram

#### **1.1 Conventions**

- #Abc is used to indicate a signal that is active when pulled low: for example, #Reset.

- Logic level one is a voltage that corresponds to Boolean true (1) state.

- Logic level zero is a voltage that corresponds to Boolean false (0) state.

- To set a bit or bits means to establish logic level one.

- To clear a bit or bits means to establish logic level zero.

- A *signal* is an electronic construct whose state conveys or changes in state convey information.

- A *pin* is an external physical connection. The same pin can be used to connect a number of signals.

- Asserted means that a discrete signal is in active logic state.

- Negated means that an asserted discrete signal changes logic state.

- LSB means *least significant bit* or *bits*, and MSB means *most significant bit* or *bits*. References to low and high bytes or words are spelled out.

- Numbers ended in letter *B* are binary. Numbers preceded by *0x* are hexadecimal.

## 1.2 Features

To support a wide variety of applications, AK3671 boasts a robust array of features, including the following:

- 32-bit microprocessor core, integrated I/D cache with MMU capability

- up to 184MHz CPU clock and 92MHz system operating frequency

- advanced power management module

- high-efficient PMU, including one DC-DC regulator and one LDO

- supports little endian only

- supports 64MB SDRAM

- supports up to two pieces of NAND FLASH with ECC function (hardware generation, detection, indication and software correction)

- embedded audio processor with real-time AMR codec/ MP3 decoder/ WMA decoder/ 64-tone MIDI synthesizer/AAC decoder/AAC+ decoder, supporting audio stream in PCM/ADPCM format

- H.263 decoder and encoder, CIF30fps@60MHz

- MJPEG decoder and encoder, CIF30fps@60MHz

- MPEG4-SP. level 1, 2&3 decoder and encoder, CIF30fps@60MHz

- JPEG decoder and encoder

- software I2C

- CCIR 601/CCIR 656 CMOS image sensor interface with programmable image size

and smart scaling capability

- 16-bit/9-bit/8-bit MPU display with programmable LCD size

- one 16-bit sigma-delta ADC for voice recording

- one 10-bit ADC including four channels for touch screen, one channel for battery measurement, and one general-purpose input channel

- two 18-bit Sigma-Delta DACs for stereo speakers

- Class AB power amplifier (620mW maximum output at SPVDD =3.6V)

- built-in headphone driver

- built-in vibrator and LED control in synchronization with music

- master/slave I2S interface

- one UART

- one SPI (master or slave operation)

- MMC/SD interface, MMC 4.0; SD 2.0

FO

- USB 2.0 HS Device

- Thirty-one GPIOs, three dedicated, twenty-eight as GPIOs and shared with other pins

- JTAG supporting in-circuit debugging

- on-chip PLL and 32.768KHz RTC

- one PWM

- three General Purpose timers

- one watchdog timer

- one RTC watchdog timer

- four bootstrap modes

- package:

AK3671: 144-pin QFP

AK3671B: 144-pin BGA

## **1.3 Target Applications**

The AK3671 targets Portable Media Players (PMPs), Electronic Learning Machines (ELMs), digital audio/video players, portable handheld devices, and other advanced multimedia appliances.

## **1.4 Product Documentation**

The following document(s) is (are) required for a complete description of the AK3671(B) and are necessary to design properly with the device.

• AK3671(B) Programmer's Guide

## 1.5 Ordering Information

| PART NUMBER  | PACKAGE TYPE | OPERATING VOLTAGE | ORDER<br>NUMBER |

|--------------|--------------|-------------------|-----------------|

| AK3671Q144   | 144 pip OED  | I/O: 2.97V~3.63V, |                 |

| AK307 IQ144  | 144-pin QFP  | core: 1.62~1.98V  |                 |

| AK3671B144   | 144 pip PCA  | I/O: 2.97V~3.63V, |                 |

| AK307 ID 144 | 144-pin BGA  | core: 1.62~1.98V  |                 |

.

## 2 Signals and Connections

## 2.1 Pin Definitions

Table 2-1 identifies and describes the AK3671 signals that are assigned to package pins. The pin definitions are grouped by the internal modules they are connected to.

| PIN NAME               | DIRECTION     | ANALOG/<br>DIGITAL | PULLUP<br>/PULLDOWN | RESET | DESCRIPTION                                                                                                                                                    |  |  |  |

|------------------------|---------------|--------------------|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1. Reset and Clock (8) |               |                    |                     |       |                                                                                                                                                                |  |  |  |

| #RST                   | I             | D                  | PU                  | 1     | System reset, external active low<br>Schmitt trigger input signal. When this<br>signal is active, all modules (with the<br>exception of RTC module) are reset. |  |  |  |

| watch_dog              | 0             | D                  | PPU                 | I/PU  | Watchdog timer (Timer 4) has reached 0 state indicator, low active.                                                                                            |  |  |  |

| XTAL12MI               | I             | D                  |                     |       | External 12MHz crystal input.                                                                                                                                  |  |  |  |

| XTAL12MO               | 0             | D                  | -                   | -     | External 12MHz crystal output.                                                                                                                                 |  |  |  |

| PCLK_OUT               | 0             | D                  | PPU                 | 0     | A programmable clock output, controlled by Clock Divider Register.                                                                                             |  |  |  |

| XTAL32KI               | I             | D                  | -                   | -     | External 32.768KHz crystal input.                                                                                                                              |  |  |  |

| XTAL32KO               | 0             | D                  | -                   | -     | External 32.768KHz crystal output.                                                                                                                             |  |  |  |

| RTC_WU_WD              | 0             | D                  | -                   | O/Z   | RTC wakeup/watch dog indicator for<br>power control processing (active high<br>pulse indicator to Power Supply.)                                               |  |  |  |

| 2. USB2.0 Interfac     | ce (4)        |                    |                     |       |                                                                                                                                                                |  |  |  |

| DP                     | I/O           | А                  |                     | -     | USB Data pin, Data+.                                                                                                                                           |  |  |  |

| DM                     | 1/0           | A                  | -                   | -     | USB Data pin, Data                                                                                                                                             |  |  |  |

| VDDA                   | I/O           | A                  | -                   | -     | This pin should tie a 0.1u capacitor to VSS(USB).                                                                                                              |  |  |  |

| RREF                   | I/O           | A                  | -                   | -     | External reference pin. It is recommended to connect a 10K ohm external reference resistor, with 1% tolerance to analog ground.                                |  |  |  |

| 3. Audio/Analog In     | iterface (18) |                    |                     |       |                                                                                                                                                                |  |  |  |

Table 2-1 AK3671 Functional Pin Definitions

| PIN NAME | DIRECTION | ANALOG/<br>DIGITAL | PULLUP<br>/PULLDOWN | RESET | DESCRIPTION                                                                                                                                                                              |

|----------|-----------|--------------------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R100K_TS | I/O       | A                  | -                   | -     | Reference PIN, connecting an external 100K-ohm resistor between this pin and ground. The resistor employed here is to provide a bias current for the Opamp(ADC's internal amplifier).    |

| VCM      | I         | A                  | -                   | -     | ADC2 mid rail voltage decoupling<br>input. It is recommended to parallel<br>connect a 10uF capacitor and a 0.1uF<br>capacitor between this pin and<br>ground. Voltage level is 1/2 AVDD. |

| HPL      | 0         | А                  | -                   | -     | Audio headphone left output.                                                                                                                                                             |

| HPR      | 0         | А                  | -                   |       | Audio headphone right output.                                                                                                                                                            |

| Line_in  | I         | A                  | -                   |       | Mono line in.                                                                                                                                                                            |

| SPKPLUS  | 0         | A                  | -                   | -     | Audio speaker differential output plus.                                                                                                                                                  |

| SPKMINUS | 0         | А                  |                     | -     | Audio speaker differential output minus.                                                                                                                                                 |

| MIC_IN   | I         | А                  |                     | -     | Microphone single end input.                                                                                                                                                             |

| MIC_P    | I         | A                  |                     |       | Differential microphone positive input.<br><b>Note</b> : If single end input microphone is used, leave this pin unconnected.                                                             |

| MIC_N    |           | A                  |                     | -     | Differential microphone negative<br>input.<br><b>Note</b> : If single end input microphone<br>is used, leave this pin unconnected.                                                       |

| AD0      | I         | A                  |                     | -     | A/D input node 1, or providing 3.3V<br>output under software control;<br>connecting to XP (X positive) channel<br>of touch panel.                                                        |

| AD1      | Ι         | A                  | -                   | -     | A/D input node 2, or providing 0V<br>output under software control;<br>connecting to XN (X negative)<br>channel of touch panel.                                                          |

| PIN NAME   | DIRECTION | ANALOG/<br>DIGITAL | PULLUP<br>/PULLDOWN | RESET | DESCRIPTION                                                                                                                                                                                                                                                           |

|------------|-----------|--------------------|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD2        | I         | A                  | -                   | -     | A/D input node 3, or providing 3.3V<br>output under software control;<br>connecting to YP (Y positive) channel<br>of touch panel.                                                                                                                                     |

| AD3        | I         | A                  | -                   | -     | A/D input node 4, or providing 0V<br>output under software control;<br>connecting to YN (Y negative)<br>channel of touch panel.                                                                                                                                       |

| AIN        | I         | А                  | -                   | -     | A general-purpose AD input channel.                                                                                                                                                                                                                                   |

| BANDGAP    | I/O       | A                  | -                   | -     | Reference voltage of 1.4V, connecting to an external 10uF and 0.1uF capacitance.                                                                                                                                                                                      |

| DC_SW18    | I/O       | A                  | -                   | 0.5   | Switch output from DC-DC.<br>A 10uH inductor should be connected<br>between this pin and the pin<br>DC_V18O.                                                                                                                                                          |

| DC_V18O    | I/O       | A                  | <u>co</u>           | -     | 300mA output current load potential.<br>It is used for digital 1.8V blocks<br>applications and its voltage can be<br>adjusted from 1.5V to 1.8V.<br>It is recommended to connect a 10uF<br>capacitor between this pin and<br>ground.                                  |

| LDO_V33A_O | 0         | A                  | 201                 | -     | <ul> <li>3.3V output for analog applications,</li> <li>300mA output current load potential.</li> <li>The output voltage can be adjusted from 2.7V to 3.3V</li> <li>It is recommended to parallel connect two 2.2uF capacitors between this pin and ground.</li> </ul> |

| LDO_V33D_O | Ο         | A                  | -                   | -     | <ul><li>3.3V output for digital applications,</li><li>300mA output current load potential.</li><li>The output voltage can be adjusted</li></ul>                                                                                                                       |

| PIN NAME                | DIRECTION       | ANALOG/<br>DIGITAL | PULLUP<br>/PULLDOWN                             | RESET                                                    | DESCRIPTION                                                                                                        |  |

|-------------------------|-----------------|--------------------|-------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

|                         |                 |                    |                                                 |                                                          | from 2.7V to 3.3V<br>It is recommended to parallel connect<br>two 2.2uF capacitors between this pin<br>and ground. |  |

| HAVDD_DCAP              | I/O             | А                  | -                                               | -                                                        | Connected a capacitor(optional)                                                                                    |  |

| 4. CMOS Image S         | ensor Interface | (12)               |                                                 |                                                          |                                                                                                                    |  |

| VISCLK                  | 0               | D                  | PPU                                             | I/PU                                                     | Programmable frequency from dividing ASIC CLK.                                                                     |  |

| VIVREF                  | I               | D                  | PPU                                             | I/PU                                                     | Vertical sync signal from camera.                                                                                  |  |

| VIHREF                  | I               | D                  | PPU                                             | I/PU                                                     | Horizontal sync signal from camera.                                                                                |  |

| VIPCLK                  | I               | D                  | PPU                                             | I/PU                                                     | Pixel clock from camera.                                                                                           |  |

| VIPIXEL[7:0]            | I               | D                  | VIPIXEL[7:5]:<br>PPU<br>VIPIXEL[4:0]:<br>PPD    | [7:5] I/PU<br>[4:0] I/PD                                 | Pixel data, supporting YCbCr4:2:2 format data which is compliant with CCIR601/CCIR656.                             |  |

| 5. LCD Display Inte     | erface (20)     |                    |                                                 |                                                          |                                                                                                                    |  |

| #MPU_CS                 | 0               | D                  |                                                 | 0                                                        | LCD chip select.                                                                                                   |  |

| MPU_A0                  | 0               | D                  | 6                                               | 0                                                        | Data / command select:<br>Low: command.<br>High: display data.                                                     |  |

| #MPU_RD                 | 0               | D                  | -                                               | 0                                                        | Read enable.                                                                                                       |  |

| #MPU_WR                 | 0               | D                  | -                                               | 0                                                        | Write enable.                                                                                                      |  |

| MPU_AD[15:0]            | 1/0             | D                  | PPU:<br>AD[15:10],<br>AD[7:0];<br>PPD: AD[9:8]; | [15:11]<br>I/PU<br>[10] O/PU<br>[9:8] I/PD<br>[7:0] I/PU | Address/data bus.                                                                                                  |  |

| 6. SDRAM Interface (39) |                 |                    |                                                 |                                                          |                                                                                                                    |  |

| #MCS                    | 0               | D                  | -                                               | 0                                                        | SDRAM chip select.                                                                                                 |  |

| MCLK                    | 0               | D                  | -                                               | 0                                                        | Main clock (synchronized with respect to internal clock tree).                                                     |  |

| MADDR[12:0]             | 0               | D                  | -                                               | 0                                                        | Address bus.                                                                                                       |  |

Publication Release Date: October, 2009

| PIN NAME                | DIRECTION  | ANALOG/<br>DIGITAL | PULLUP<br>/PULLDOWN                                                     | RESET                                                   | DESCRIPTION                                                                                                                               |

|-------------------------|------------|--------------------|-------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| MDATA[15:0]             | I/O        | D                  | PPU                                                                     | I/PU                                                    | Memory data bus.                                                                                                                          |

|                         |            |                    |                                                                         |                                                         | Bank select address,                                                                                                                      |

| MBA[1:0]                | ο          | D                  | -                                                                       | Ο                                                       | Selecting bank to be activated during<br>row address latch time; or selecting<br>bank for read/write during column<br>address latch time. |

| MRAS                    | 0          | D                  | -                                                                       | 0                                                       | Latching row addresses on the positive going edge of the CLK with RAS low.                                                                |

| MCAS                    | 0          | D                  | -                                                                       | ο                                                       | Latching column addresses on the positive going edge of the CLK with CAS low.                                                             |

| #MBE[1:0]               | 0          | D                  | -                                                                       | 0                                                       | Byte enable, active low.[0] controls<br>low byte,[1] controls high byte                                                                   |

| #MWR                    | 0          | D                  | -                                                                       | 0                                                       | Write enable, active low.                                                                                                                 |

| MCKE                    | 0          | D                  |                                                                         | ο                                                       | Clock enable, for SDRAM power saving.                                                                                                     |

| 7. Nand Flash Inte      | rface (14) |                    |                                                                         |                                                         |                                                                                                                                           |

| NFC_data[7:0]           | I/O        | D                  | PPU                                                                     | I/PU                                                    | Nand Flash data bus.                                                                                                                      |

| #NFC_CE[0]              | 0          | D                  | -                                                                       | 0                                                       | Nand Flash chip enable signal 0.                                                                                                          |

| #NFC_CE[1]              | I/O        | D                  | PPU                                                                     | I/PU                                                    | Nand Flash chip enable signal 1.                                                                                                          |

| NFC_ALE                 | I/O        | D                  | PPD                                                                     | I/PD                                                    | Nand Flash address latch enable.                                                                                                          |

| NFC_CLE                 | I/O        | D                  | PPD                                                                     | I/PD                                                    | Nand flash command latch enable.                                                                                                          |

| #NFC_WR                 | 1/0        | D                  | PPU                                                                     | O/PU                                                    | Nand flash write enable.                                                                                                                  |

| #NFC_RD                 | I/O        | D                  |                                                                         | 0                                                       | Nand flash read enable.                                                                                                                   |

| 8. GPIO(31)             |            |                    |                                                                         |                                                         |                                                                                                                                           |

| GPIO[31:8]<br>GPIO[6:0] | I/O        | D                  | PPU:<br>GPIO[30:23],<br>GPIO[17:16],<br>GPIO[14:5],<br>GPIO[3];<br>PPD: | [31] I<br>[30:23]<br>I/PU<br>[22:18]<br>I/PD<br>[17:16] | General input/output ports.<br><b>Notes:</b><br>* Apart from the GPIO[29:28], all the<br>GPIO ports can be used as wake-up<br>ports.      |

| PIN NAME            | DIRECTION | ANALOG/<br>DIGITAL | PULLUP<br>/PULLDOWN | RESET        | DESCRIPTION                                            |

|---------------------|-----------|--------------------|---------------------|--------------|--------------------------------------------------------|

|                     |           |                    | GPIO[22:18],        | I/PU         |                                                        |

|                     |           |                    | GPIO[15]            | [15] I/PD    |                                                        |

|                     |           |                    | GPIO[4],            | [14] O       |                                                        |

|                     |           |                    | GPIO[2];            | [13:8],[6:5] |                                                        |

|                     |           |                    | NO PPU,PPD:         | I/PU         |                                                        |

|                     |           |                    | GPIO[31],           | [4] I/PD     |                                                        |

|                     |           |                    | GPIO[1:0]           | [3] I/PU     |                                                        |

|                     |           |                    |                     | [2] I/PD     |                                                        |

|                     |           |                    |                     | [1:0] I      |                                                        |

| 9. PWM (1)          | Γ         |                    |                     |              |                                                        |

| PWM                 | I/O       | D                  | PPD                 | I/PD         | Pulse-width modulated output signal for PWM.           |

| 10.I2S Interface (3 | 3)        |                    |                     |              |                                                        |

| I2S_BCLK            | I/O       | D                  | PPU                 | I/PU         | I2S bit clock.                                         |

| I2S_LRCLK           | I/O       | D                  | PPU                 | I/PU         | I2S channel selection.                                 |

| I2S_DIO             | I/O       | D                  | PPU                 | I/PU         | I2S serial data input/output.                          |

| 11. UART/MMC/S      | PI (16)   |                    |                     |              |                                                        |

| UTD                 | 0         | D                  | PPU                 | I/PU         | Transmit data bit of UART.                             |

| URD                 | I         | D                  | PPU                 | I/PU         | Receive data bit of UART.                              |

| МСК                 | 0         | D                  | -                   |              | MMC/SD operating clock.                                |

| MCMD                | I/O       | D                  | - //                | 0            | MMC/SD command.                                        |

| MMC_data[7:0]       | I/O       | D                  | PPU                 | I/PU         | MMC/SD data bus.                                       |

| #SPI_CS             | 1/0       | D                  | PPU                 | I/PU         | SPI chip select, active low.                           |

| SPI_CLK             | 1/0       | D                  | PPD                 | I/PD         | SPI clock.                                             |

| SPI_MOSI            | I/O       | D                  | PPD                 | I/PD         | In host mode, data output; in client mode, data input. |

| SPI_MISO            | I/O       | D                  | PPU                 | O/PU         | In host mode, data input; in client mode, data output. |

| 12. JTAG (5)        |           |                    |                     |              |                                                        |

| #TRST               | I         | D                  | -                   | I            | JTAG logic reset.                                      |

| TMS                 | I/O       | D                  | PPU                 | I/PU         | JTAG mode select.                                      |

| PIN NAME           | DIRECTION | ANALOG/<br>DIGITAL | PULLUP<br>/PULLDOWN | RESET | DESCRIPTION                                                                                                           |

|--------------------|-----------|--------------------|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------|

| TCLK               | I/O       | D                  | PPU                 | I/PU  | JATG clock, less than 1 MHz, asynchronous with CLK.                                                                   |

| TDI                | I/O       | D                  | PPU                 | I/PU  | JTAG serial data input.                                                                                               |

| TDO                | I/O       | D                  | PPU                 | 0     | JTAG serial output.                                                                                                   |

| 13. Scan Control ( | 1)        |                    |                     |       |                                                                                                                       |

| SCAN_MODE          | I         | D                  | PD                  | I/PD  | Scan mode selection, connecting to LOW for normal operations.                                                         |

| 14. Power and Gro  | ound (28) |                    |                     | L     |                                                                                                                       |

| VDD                | PWR       | D                  | -                   | -     | 2                                                                                                                     |

| VDDIO              | PWR       | D                  | -                   | -     | 4                                                                                                                     |

| VSS                | GND       | D                  | -                   | -     | 3                                                                                                                     |

| VSSIO              | GND       | D                  | -                   |       | 5                                                                                                                     |

| Vbat(RTC)          | PWR       | D                  | -                   |       | 1                                                                                                                     |

| AVDD18(PLL)        | PWR       | A                  |                     | -     | PLL voltage, it is recommended to connect a 1uF capacitor and a 0.1uF capacitor parallel between this pin and ground. |

| AVSS               | GND       | А                  |                     | -     | 1                                                                                                                     |

| AVDD               | PWR       | A                  | -                   | -     | 1                                                                                                                     |

| VDD33(USB)         | PWR       | A                  | -                   | -     | 1                                                                                                                     |

| VSS(USB)           | GND       | A                  |                     | -     | 1                                                                                                                     |

| SPVSS              | GND       | A                  | -                   | -     | 2                                                                                                                     |

| SPVDD              | PWR       | A                  |                     | -     | 2                                                                                                                     |

#### Notes:

1. I----INPUT, O----OUTPUT, I/O----INPUT/OUTPUT, PWR----POWER, GND----GROUND, A ---- ANALOG, D----DIGITAL.

2. PU----PULLUP, PD----PULLDOWN: Corresponding ports have been attached pullup/pulldown function.

PPU----PROGRAMMABLE PULLUP, PPD---- PROGRAMMABLE PULLDOWN: The pullup/pull-down function attached to the corresponding ports is configurable (enabled or disabled) by corresponding registers. Default status is that the pull-up/pull-down function attached to the corresponding port is enabled.

## 2.2 Shared-Pin List

In order to reduce pin numbers, many pins are shared by two or three function blocks that would not be implemented at the same time. The table below lists the shared pins.

| MODULE        | PIN NAME    | MODULE        | PIN NAME   | MODULE             | PIN NAME    | RESET<br>STATE |

|---------------|-------------|---------------|------------|--------------------|-------------|----------------|

| Nand<br>Flash | NFC_data[0] | LCD           | MPU_AD[0]  | MMC/SD             | MMC_data[0] | NFC_data[0]    |

| Nand<br>Flash | NFC_data[1] | LCD           | MPU_AD[1]  | MMC/SD             | MMC_data[1] | NFC_data[1]    |

| Nand<br>Flash | NFC_data[2] | LCD           | MPU_AD[2]  | MMC/SD             | MMC_data[2] | NFC_data[2]    |

| Nand<br>Flash | NFC_data[3] | LCD           | MPU_AD[3]  | MMC/SD             | MMC_data[3] | NFC_data[3]    |

| Nand<br>Flash | NFC_data[4] | LCD           | MPU_AD[4]  | MMC/SD             | MMC_data[4] | NFC_data[4]    |

| Nand<br>Flash | NFC_data[5] | LCD           | MPU_AD[5]  | MMC/SD             | MMC_data[5] | NFC_data[5]    |

| Nand<br>Flash | NFC_data[6] | LCD           | MPU_AD[6]  | MMC/SD             | MMC_data[6] | NFC_data[6]    |

| Nand<br>Flash | NFC_data[7] | LCD           | MPU_AD[7]  | MMC/SD             | MMC_data[7] | NFC_data[7]    |

| GPIO          | GPIO[30]    | Nand<br>Flash | #NFC_CE[1] | -                  |             | GPIO[30]       |

| Nand<br>Flash | NFC_CLE     | LCD           | MPU_AD[8]  | SPI                | SPI_MOSI    | NFC_CLE        |

| Nand<br>Flash | NFC_ALE     | LCD           | MPU_AD[9]  | SPI                | SPI_CLK     | NFC_ALE        |

| Nand<br>Flash | #NFC_WR     | LCD           | MPU_AD[10] | SPI                | SPI_MISO    | #NFC_WR        |

| Nand<br>Flash | #NFC_RD     | MMC/SD        | MCMD       | -                  | -           | #NFC_RD        |

| GPIO          | GPIO[31]    | MMC/SD        | МСК        | -                  | -           | GPIO[31]       |

| GPIO          | GPIO[25]    | LCD           | MPU_AD[11] | -                  | -           | GPIO[25]       |

| GPIO          | GPIO[26]    | LCD           | MPU_AD[12] | -                  | -           | GPIO[26]       |

| GPIO          | GPIO[27]    | LCD           | MPU_AD[13] | -                  | -           | GPI0[27]       |

| GPIO          | GPIO[28]    | LCD           | MPU_AD[14] | -                  | -           | GPIO[28]       |

| GPIO          | GPIO[29]    | LCD           | MPU_AD[15] | -                  | -           | GPIO[29]       |

| GPIO          | GPIO[3]     | Camera        | VIPIXEL[6] | Reset<br>and clock | Watch_dog   | GPIO[3]        |

| GPIO          | GPIO[4]     | PWM           | PWM        | -                  | -           | GPIO[4]        |

| GPIO          | GPIO[5]     | Camera        | VIVREF     | -                  | -           | GPIO[5]        |

Table 2-2 Shared-Pin List

| MODULE | PIN NAME | MODULE             | PIN NAME   | MODULE | PIN NAME | RESET<br>STATE |

|--------|----------|--------------------|------------|--------|----------|----------------|

| GPIO   | GPIO[6]  | SPI                | #SPI_CS    | -      | -        | GPIO[6]        |

| GPIO   | GPIO[8]  | Camera             | VIHREF     |        |          | GPIO[8]        |

| GPIO   | GPIO[9]  | UART               | URD        | -      | -        | GPIO[9]        |

| GPIO   | GPIO[10] | UART               | UTD        | -      | -        | GPIO[10]       |

| JTAG   | TCLK     | I2S                | I2S_BCLK   | GPIO   | GPIO[11] | TCLK           |

| JTAG   | TMS      | I2S                | I2S_LRCLK  | GPIO   | GPIO[12] | TMS            |

| JTAG   | TDI      | I2S                | I2S_DIO    | GPIO   | GPIO[13] | TDI            |

| JTAG   | TDO      | Reset<br>and clock | PCLK_out   | GPIO   | GPIO[14] | TDO            |

| GPIO   | GPIO[16] | Camera             | VIPIXEL[7] | -      |          | GPIO[16]       |

| GPIO   | GPIO[17] | Camera             | VIPIXEL[5] | -      |          | GPIO[17]       |

| GPIO   | GPIO[18] | Camera             | VIPIXEL[4] |        | -        | GPIO[18]       |

| GPIO   | GPIO[19] | Camera             | VIPIXEL[3] |        | -        | GPIO[19]       |

| GPIO   | GPIO[20] | Camera             | VIPIXEL[2] |        | -        | GPIO[20]       |

| GPIO   | GPIO[21] | Camera             | VIPIXEL[1] | -      | -        | GPIO[21]       |

| GPIO   | GPI0[22] | Camera             | VIPIXEL[0] | -      |          | GPI0[22]       |

| GPIO   | GPIO[23] | Camera             | VISCLK     | -      |          | GPIO[23]       |

| GPIO   | GPIO[24] | Camera             | VIPCLK     | -      |          | GPIO[24]       |

## **3** Functional Description

## 3.1 PMU

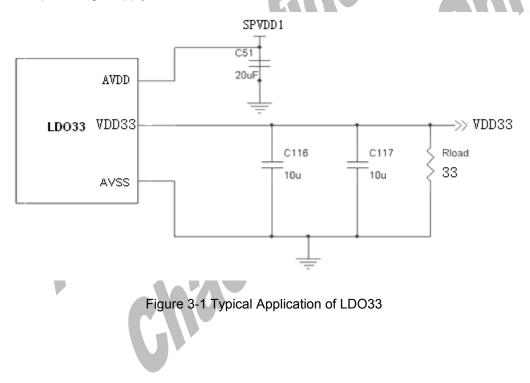

The power management unit, consisting of a step-down DC/DC regulator (BUCK18) and a LDO (LDO33), governing power functions of the AK3671 processor, is responsible for coordinating many functions, including:

- providing power to integrated circuits (both analog circuits and digital circuits)

- monitoring power connections

#### 3.1.1 LDO and DC/DC Regulator

The embedded low-dropout regulator is used to power the internal analog circuits and digital circuits. The LDO provides 200mA output current and over-current protection.

Promising an efficiency of 83 percent, the step-down DC/DC regulator operates at 1000KHz and accepts voltage supply between 3V and 5V.

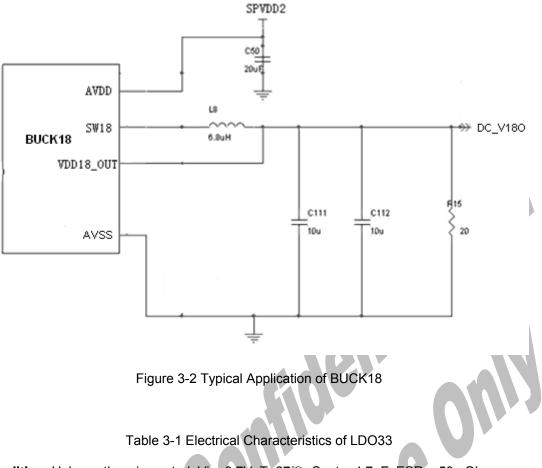

Figure 3-2 Typical Application of BUCK18

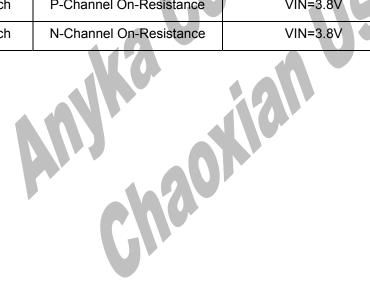

| Table 3-1 | Electr | ical | Cha | arac | teristics | of LDO3 | 3 |

|-----------|--------|------|-----|------|-----------|---------|---|

|           |        |      |     |      |           |         |   |

| SYMBOL                      | PARAMETER                | CONDITIONS        | MIN | ТҮР | MAX | UNIT |

|-----------------------------|--------------------------|-------------------|-----|-----|-----|------|

| Vin                         | Input voltage            | -                 | 3.5 | 3.8 | 5   | V    |

| Vout (accuracy)             | Output voltage           | Default           | -3  | -   | +3  | %    |

| Vout                        | Output voltage           | - /               | -   | 3.3 | -   | V    |

| lout                        | Output current           | -                 | -   | -   | 200 | mA   |

| riangleVout,                | Load regulation          | T=27 ℃, Vin=3.3V, | -   | 40  | -   | mV   |

| ∆Vout/∆Iout                 | Load regulation          | @lout=1 to 100mA  |     | 340 | -   | mOhm |

|                             |                          | lout=1mA          | -   | 2   | -   | mV   |

| riangleVout,                | Line regulation          | @Vin=3.3V to 5V   | -   | 0.2 | -   | %    |

| riangleVout/ $	riangle$ Vin | Line regulation          | lout=100mA(MAX)   | -   | 6   | -   | mV   |

|                             |                          | @Vin=3.0V to 5V   | -   | 0.5 | -   | %    |

| lcc                         | Vin Quiescent<br>Current | No load           | -   | 50  | -   | uA   |

| lpd                         | Power-down               | -                 | -   | 0.1 | -   | uA   |

| SYMBOL | PARAMETER | CONDITIONS | MIN | ТҮР | MAX | UNIT |

|--------|-----------|------------|-----|-----|-----|------|

|        | current   |            |     |     |     |      |

Note: Load Transient Response settle-up time tolerances 0.1% difference of final Vout value.

#### Table 3-2 Electrical Characteristics of DC/DC

**Condition**: Unless otherwise noted, typical values are at  $T_A = +27^{\circ}C$  and all Current Values are dynamic.

| SYMBOL                   | PARAMETER                | CONDITION                         | ТҮР.    | UNIT |

|--------------------------|--------------------------|-----------------------------------|---------|------|

| V <sub>IN</sub>          | Operating Supply Voltage | I <sub>LOAD_max</sub> =200mA      | 3~5     | V    |

| V <sub>OUT</sub>         | Output Voltage           | 0mA <i<sub>LOAD&lt;200mA</i<sub>  | 1.5~1.8 | V    |

| I <sub>LOAD_MAX</sub>    | MAX Output Current       | 3.0V <v<sub>IN&lt;5.0V</v<sub>    | 200     | mA   |

| I <sub>ON_LOAD</sub>     | Vin Quiescent Current    | I <sub>LOAD</sub> = 0mA           | <150    | uA   |

| I <sub>powerdown</sub>   | Vin Shutdown Current     | 27°C                              | <1      | uA   |

| V <sub>ripple</sub>      | Output Voltage Ripple    | I <sub>LOAD</sub> =100mA,ESR<40mΩ | <40     | mV   |

| η                        | Efficiency               | I <sub>LOAD</sub> =80mA           | 83      | %    |

| OSC <sub>Frequence</sub> | OSC Frequency            | 27°C                              | 1000    | kHz  |

| I <sub>Limit</sub>       | Peak Current Limit       | 27°C                              | 700     | mA   |

| Rpswitch                 | P-Channel On-Resistance  | VIN=3.8V                          | 500     | mΩ   |

| Rnswitch                 | N-Channel On-Resistance  | VIN=3.8V                          | 500     | mΩ   |

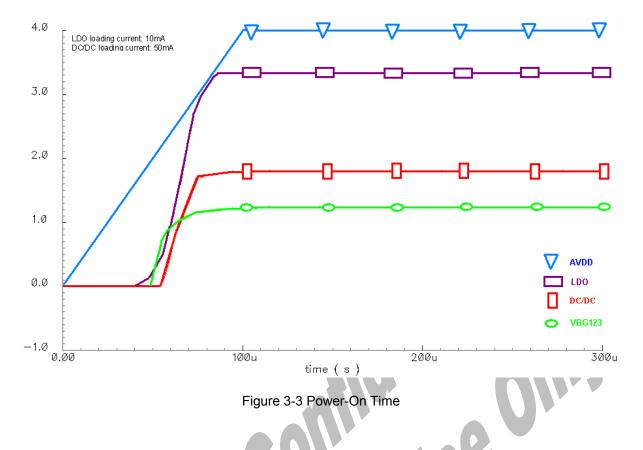

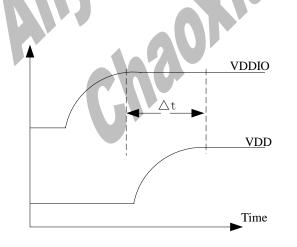

#### 3.1.2 Typical Power-On Time

#### 3.1.3 Temperature Detector

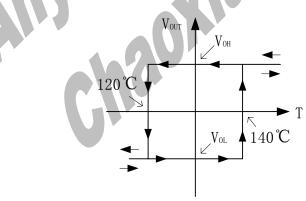

The temperature detector monitors the processor's temperature, and generates an interrupt to the CPU core when the temperature is beyond the allowable temperature range. As shown in Figure 3-4, when the temperature is rising, if the temperature reaches  $140^{\circ}$ C, an interrupt will be generated; and when the temperature is falling, if the temperature is below  $120^{\circ}$ C, an interrupt will be generated too.

Figure 3-4 Temperature Status

## 3.2 System Control

#### 3.2.1 Clock Generation and Control

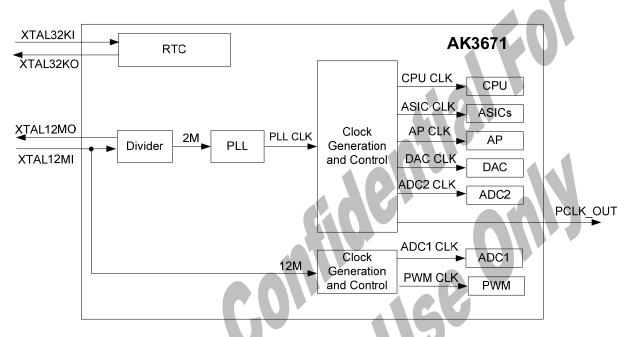

Figure 3-5 illustrates the internal clock generation and control of the AK3671 processor. In normal operation, the AK3671 accepts two possible crystals: 32.768KHz and 12MHz. The former is input from the pin XTAL32KI and generates a precise clock for the RTC module; while the latter is input from the pin XTAL12MI and generates working clocks for all the modules with the exception of RTC.

Figure 3-5 Clock Generation and Control

#### Notes:

1. CPU CLK is the working frequency of CPU core. It may be equal to ASIC CLK or twice of the ASIC CLK.

2. ASICs refer to all the functional blocks with the exception of CPU core, audio processor, I2S master and slave interfaces, ADCs and DACs. The ASIC CLK just provides a clock to the ASICs. The working frequency for a given functional block is programmable.

3. AP CLK provides working frequency to audio processor and I2S slave interface.

4. DAC CLK provides working frequency to DACs and I2S master interface.

5. ADC1 CLK is the working frequency of the ADC used for touch screen and battery measurement.

6. ADC2 CLK is the working frequency of the ADC used for voice recording.

7. PCLK\_OUT is a programmable clock output.

8. PWM CLK provides working clock to PWM.

9. PLL can be powered down when the system is in standby mode or power down mode. Then the CPU CLK, ASIC CLK, AP CLK, ADC2 CLK, DAC CLK and PCLK\_out are off.

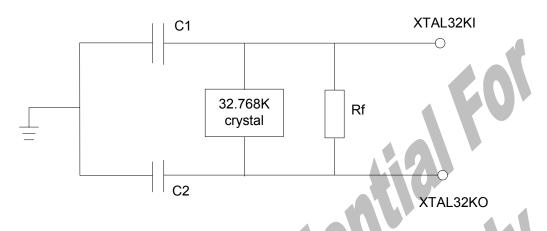

10. The external connection of the pins XTAL32KI and XTAL32KO is quite strict. Figure 3-6 gives a typical connection; and Table 3-3 recommends the values of critical parameters.

Figure 3-6 A Typical Connection Between XTAL32KI and XTAL32KO

Table 3-3 Recommended Parameters

| ITEM | MIN | ТҮР | МАХ | UNIT  |

|------|-----|-----|-----|-------|

| Rf   | 1   | 2   | 3   | M ohm |

| C1   | 25  | 30  | 40  | pF    |

| C2   | 25  | 30  | 40  | pF    |

All the clocks mentioned above are configurable by software and the relationships with PLL CLK are as follows:

Table 3-4 Main Clock and Internal Clocks

| ITEM     | RELATIONSHIP WITH PLL CLOCK                                    | NOTE                                                                                   |

|----------|----------------------------------------------------------------|----------------------------------------------------------------------------------------|

| PLL CLK  | When the system is reset, PLL CLK is set to 120MHz by default. | Ranging from 120MHz to 184MHz,<br>PLL CLK is configurable with step<br>length of 4MHz. |

| ASIC CLK | ASIC CLK = $\frac{PLLCLK}{2^n}$ (n=1,2,,7)                     | -                                                                                      |

| ITEM        | RELATIONSHIP WITH PLL CLOCK                                | NOTE                                                                                                                                                                   |

|-------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU CLK     | CPU CLK = ASIC CLK or<br>CPU CLK = 2 X ASIC CLK            | Under software control, CPU CLK<br>can be equal to ASIC CLK or twice<br>of the ASIC CLK.                                                                               |

| AP CLK      | AP CLK = $\frac{PLLCLK}{2^n}$ (n=1,2,,7)                   | AP CLK must be faster than or equal to ASIC CLK.                                                                                                                       |

| PCLK_out    | PCLK_out = $\frac{PLLCLK}{N}$ (N=2, 3,,2 <sup>7</sup> )    | When the system is reset, the pin PCLK_OUT outputs a clock that is equal to $\frac{mainclk}{128}$ . Software may disable the clock output if such clock is not needed. |

| ADC1<br>CLK | ADC1 CLK = $\frac{12M}{N+1}$ (N=0, 1,,2 <sup>4</sup> )     | Recommended value is 4MHz.                                                                                                                                             |

| ADC2<br>CLK | ADC2 CLK = $\frac{PLLCLK}{N+1}$ (N=0,1,,2 <sup>7</sup> )   |                                                                                                                                                                        |

| DAC CLK     | DAC CLK = $\frac{PLLCLK}{N+1}$ (N=0,1, 2,,2 <sup>6</sup> ) | DAC CLK is recommended to range from 10MHz to 18MHz.                                                                                                                   |

#### 3.2.2 Reset Module

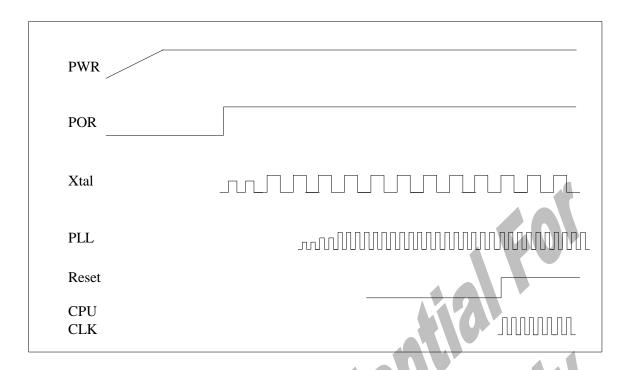

The #RST signal, when asserted low, puts all internal states (with the exception of RTC module) into predefined values. Figure 3-7 shows the reset timing of AK3671.

chaon

#### Figure 3-7 AK3671 Power On Reset Timing

Excluding PWM module, all modules contained in the AK3671 processor can be reset independently by software.

#### 3.2.3 Interrupt Module

The interrupt module collects interrupt requests from the ASICs and provides an interface to the CPU core. The CPU responds to the interrupts according to two principles:

1) priority, if multiple interrupt requests are sent at the same time;

The interrupt module supports both fast and normal interrupts, and of course the fast interrupts get the higher priority.

2) whether the interrupt has been masked or not.

The interrupt module can mask/unmask every interrupt source of normal and fast interrupts with specific bit of mask registers. Only the interrupt requests from unmasked interrupt source are responded.

The ASIC continually sends the interrupt request until it is informed by software that its request has been responded. Besides, it should be noted that when an ASIC interrupt is being processed, the interrupt is masked until the interrupt process has been finished. That is,

AK3671 cannot respond to two interrupts concurrently even though the interrupts are requested by the same ASIC.

#### 3.2.4 Bootstrap Module

When the AK3671 processor is reset, all ASIC units except GPIOs, UART, and JTAG are disabled, and the CPU core gets its first instruction from address 32'0x0000, 0000, which belongs to the on-chip ROM address space. It first reads the value of GPIO[4] to judge the boot up mode. If GPIO[4] is asserted ("1"), the AK3671 is boot up from USB port; if GPIO[4] is de-asserted ("0"), the AK3671 reads data from Nand Flash and Serial Flash in succession, and checks the password. If the password is matched, AK3671 is boot up from Nand Flash or Serial Flash. If not, AK3671 is boot up from Mass Storage.

**Note**: GPIO[4] can be used as a general purpose output port after the system has been booted up from USB port.

#### 3.2.5 Power Management

AK3671 implements a simple and powerful power control mechanism, unit clock enable. During normal operation, only the clock for CPU core and the memory controller is turned on; all ASIC accelerator units are turned off their clock inputs. An accelerator is clocked on only when it is needed, and it is immediately clocked off after its use has been finished. All internal memories are in LOW-POWER state, except when they are accessed.

#### 3.2.6 Working Modes

There are three working modes for the AK3671 processor:

#### 1) Normal operating

All the functional blocks are clocked on/off in accordance with specific operating requirement.

2) Standby

The RTC module is clocked on, PLL is powered down and other modules (including CPU core) are clocked off.

#### 3) Power down

The RTC module is powered on, and other modules (including CPU core) are powered down.

#### 3.2.7 JTAG

JTAG is AK3671's major software debugging tool. The JTAG of AK3671 supports breakpoints, controlling, monitoring and real-time running otherwise.

## 3.3 RTC Module

The RTC module accepts solely the working clock from external 32.768KHz crystal. While the system is powered off, it may be driven by the backup battery that supplies power through the pin Vbat (RTC).

The RTC module provides following functions::

- real-time clock

- alarms or wake-up signals in standby mode

- alarms in power down mode

- interrupts in normal operating mode

- a RTC watchdog timer

An alarm or an interrupt may be set by accessing corresponding registers and loading the exact time that the alarm/interrupt should be generated.

The AK3671 processor can be woken up on one of the following two conditions:

- 1. 32.768KHz clock alarm time is met

- 2. wake-up signal width >10 ASIC CLKs

#### Notes:

- 1) Apart from GPIO[29:28], all the GPIO ports can be used as wake-up ports;

- 2) Wakup signal may be high active or low active.

## 3.4 CPU core

The 32-bit RISC microprocessor core is designed specifically for high performance, costeffective and low power applications.

The CPU core provides following features:

- Integrated ALU (Arithmetic Logic Unit) and MAC(multiply-accumulate)

- 5-stage execution pipeline

- Combined 8KB instruction and data cache

- Memory Management Unit (MMU) for multi-tasking software

- Advanced High-performance Bus (AHB) external interface

• JTAG debug

#### 3.5 Memory

#### 3.5.1 On Chip Memory

To improve the AK3671's performance, 16KB ROM is added to for booting the CPU after each reset, and 2KB RAM is included as a scratch memory for high-performance and low-power kernel applications.

#### 3.5.2 External Memory

#### 3.5.2.1 RAM Interface

The RAM controller is the bridge logic that connects an internal unit to the external SDRAM. It provides following features:

- one chip select

- supporting up to 64MB memory

- supporting self-refresh function

- external SDRAM can work at a maximum frequency of 90MHz

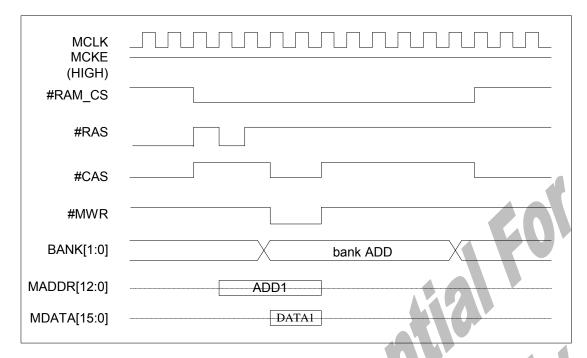

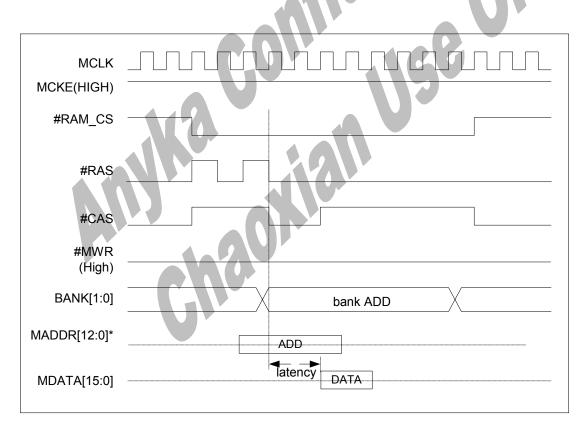

Figure 3-8 and Figure 3-9 show the write and read timing diagrams of SDRAM interface.

201

Figure 3-8 Write Timing Diagram of SDRAM Interface

Note: Only MADDR[11:0] are employed for the 8MB/16MB SDRAM.

#### Notes:

- Latency is the delay between the registration of a READ command and the availability of the first piece of output data. The latency of the SDRAM interface is fixed to 2 MCLK cycles.

- A read command is valid only when SRAM\_CS1 is low, #RAS is high, #CAS is low, and #MWR is high.

- 3. Only MADDR[11:0] are employed for the 8MB/16MB SDRAM.

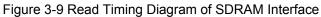

#### 3.5.2.2 Nand Flash Interface

The Nand Flash interface can connect up to 2 pieces of 8-bit wide Nand Flash concurrently regardless of Nand Flash's page size, density or organization. It provides ECC function for each piece of Nand Flash, which may be enabled or bypassed by configuring corresponding register(s).

The on-chip ECC module can correct 4/8/12/16/24/32 bits error every data block (maximum 1536B).

#### Notes:

1. Opt\_len refers to the valid period of an address, a command, or a data read/write operation. It is configurable by four bits of Command Length Register/Data Length Register, thus it ranges from 1 ASIC CLK to 16 ASIC CLKs. The default value is 16 ASIC CLKs, as shown in the figure above.

2. The rising/falling edge of ALE/CLE/#WE in a command operation is configurable respectively by four bits of Command Length Register. The default value of TS1 is "1" (the second ASIC CLK cycle); that of TF1, "13" (the fourteenth ASIC CLK cycle); that of TS2, "5" (the sixth ASIC CLK cycle); and that of TF2, "12" (the thirteenth ASIC CLK cycle).

3. The rising/falling edge of #WE/#RE in a data operation is configurable respectively by four bits of Data Length Register. The default value of TS2 for #WE is "5" (the sixth ASIC CLK cycle); that of TF2 for #WE, "12" (the thirteenth ASIC CLK cycle); that of TS2 for #RE, "5" (the sixth ASIC CLK cycle); and that of TF2 for #RE, "12" (the thirteenth ASIC CLK cycle).

## 3.6 Advanced High-performance Bus (AHB)

The AHB is a kind of high performance bus for burst data transfer. AK3671 provides two AHB channels: one is for CPU access, and the other is for debug use.

When the CPU wants to access the memory, including SDRAM and registers, it sends AHB commands to the corresponding memory controller. Then the memory controller translates the AHB commands into the signals to its module and generates the memory or register access signals to realize loading or storing data.

AHB write and read timing are fully compliant with AMBA AHB Protocol.

## 3.7 DMA/CRC Accelerator

AK3671 contains two DMA controllers: DMA controller and DMA/CRC controller. The DMA controller transfers data to/from external RAM in response to the requests generated by DMA-capable functional blocks (such as UART, SPI, etc.); while the DMA/CRC controller controls the data transfer with/without CRC between two kinds of external memories. The DMA/CRC controller is seen as a DMA-capable functional block. The data transfer does not begin until the DMA Controller has sent an ACK signal to DMA/CRC controller.

## 3.8 Register Bus Controller

The register bus controller translates AHB (Advanced High-performance Bus) transactions targeted at register space into simple WRITE and READ pulses. To simplify the interface design with AHB of CPU core, each register access is carried out in minimum 2 clock cycles.

The register bus controller also includes logic to interface with the audio processor module directly, either via audio processor I/O registers or through IDMA.

### 3.9 Video Processor

The video processor provides hardware acceleration to the compression and decompression of moving pictures and video. It supports MPEG4/H.263/M-JPEG encoding and decoding, which fully comply with *ITU-T Recommendation H.263(02/98)*, *Information technology — Coding of audio-visual objects —Part2: Visual (ISO/IEC 14496-2), and Information Technology—Digital Compression and Coding of Continuous-Tone Still Images Requirements and Guidelines (09/92)*. The performance of the video processor is:

- MPEG4 SP. Level 0,1,2&3 codec

- H.263 baseline codec

- Motion JPEG codec

#### 3.9.1 Typical Encoding Application

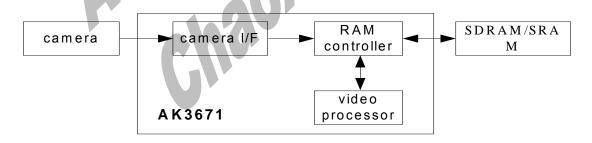

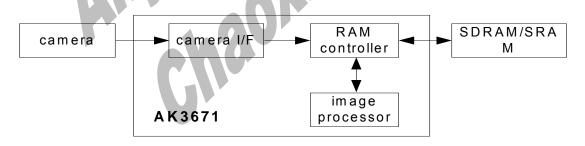

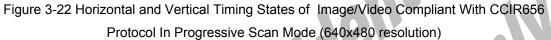

Figure 3-11 shows a typical application of the video encoding. The data from camera should be compatible with CCIR601 or CCIR656 and is stored temporarily in external RAM. Video processor encodes the data gotten from the external RAM and sends back the encoded bit stream data to the external RAM.

Revision: 0.2.0

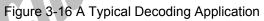

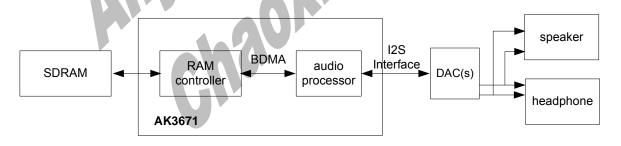

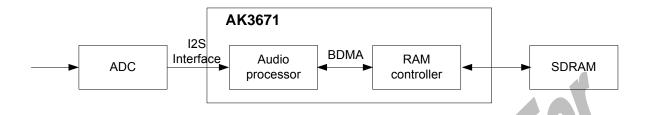

# 3.9.2 Typical Decoding Application

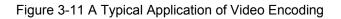

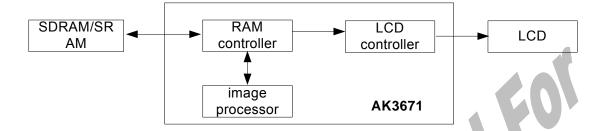

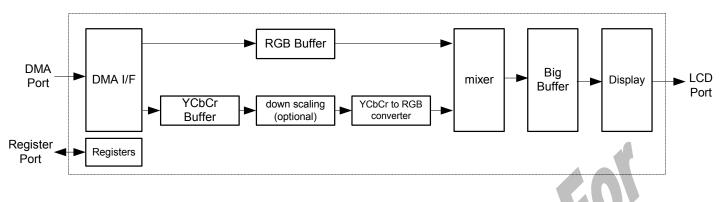

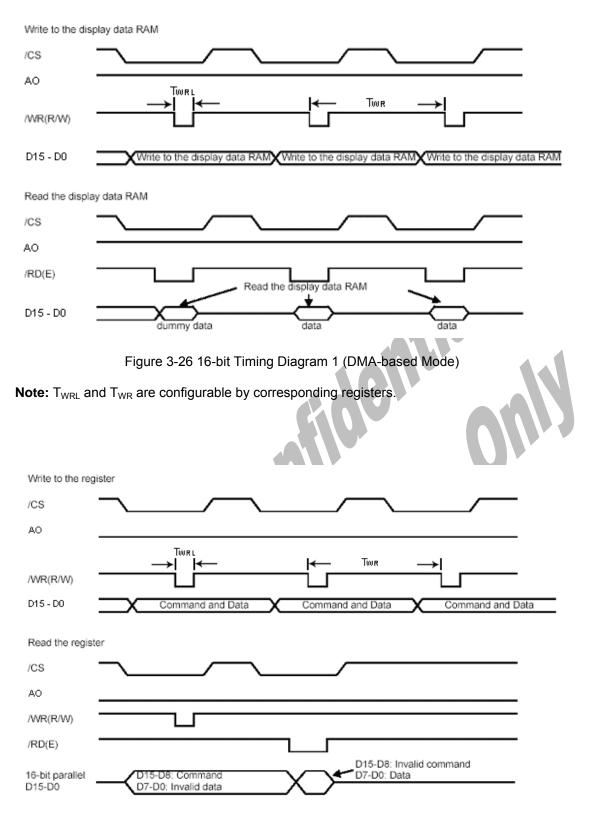

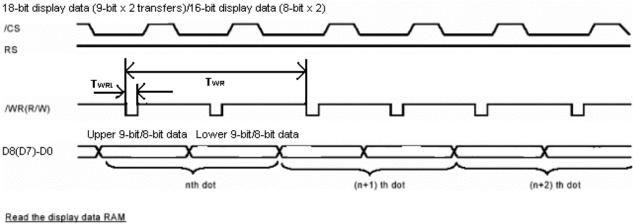

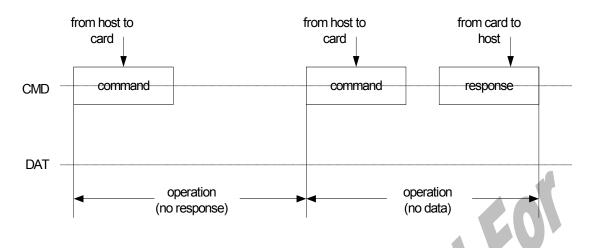

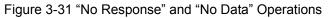

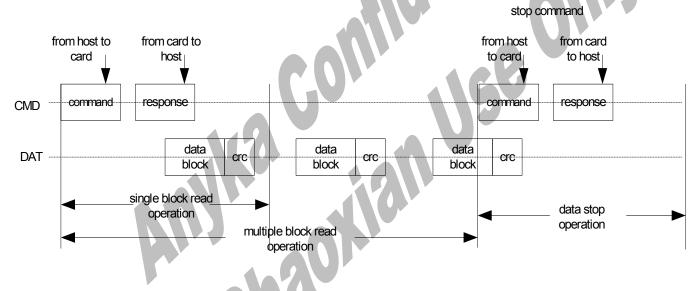

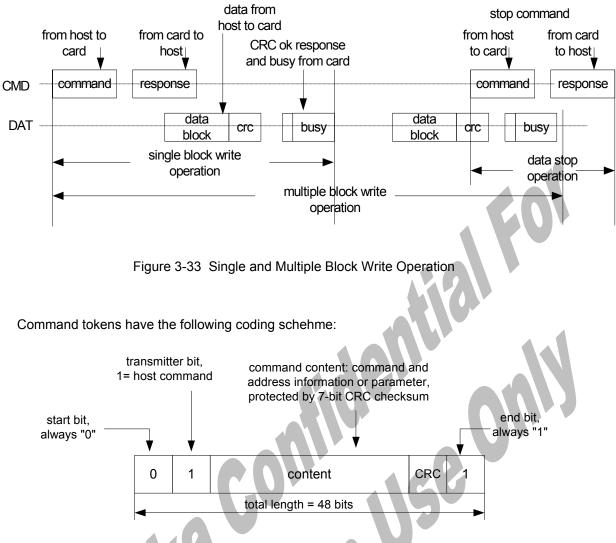

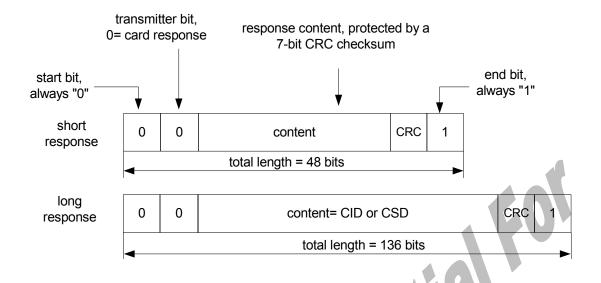

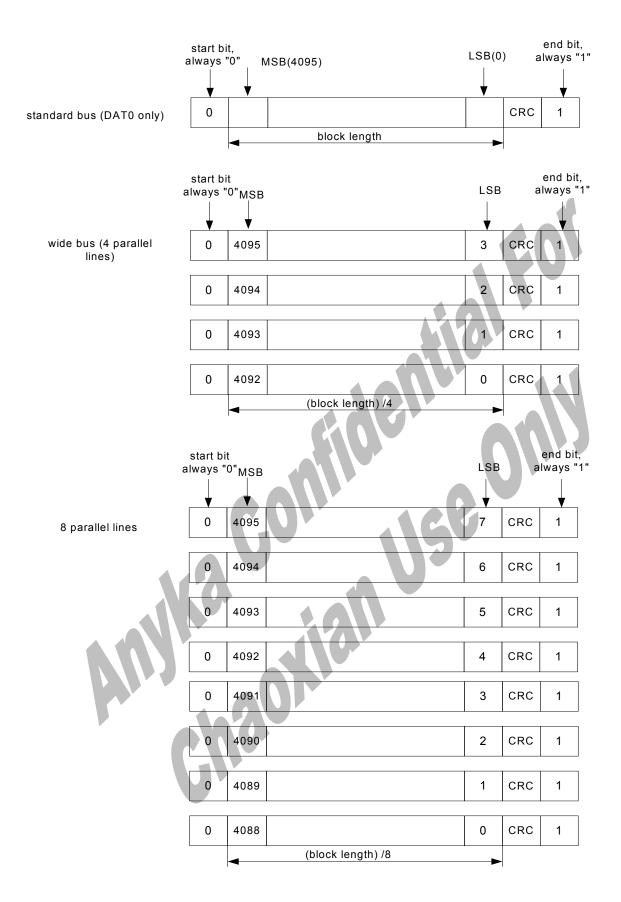

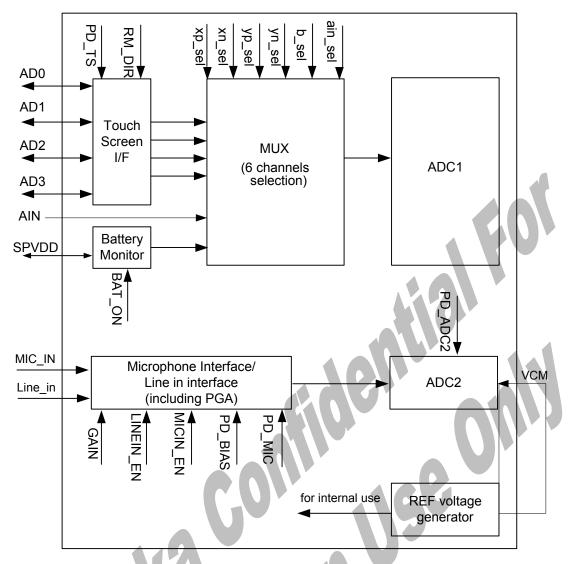

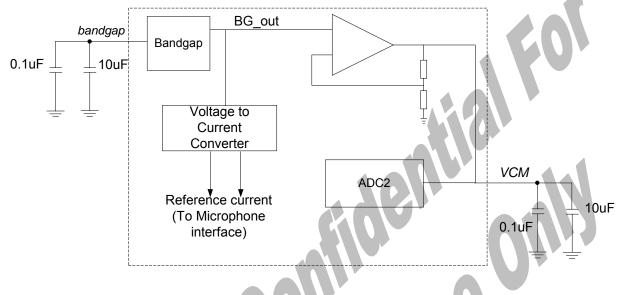

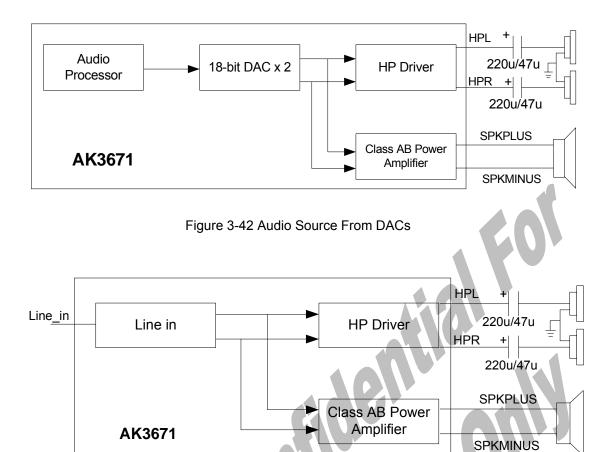

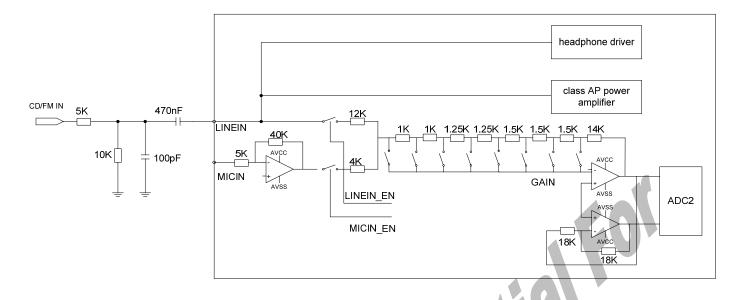

A typical application of video decoding is shown in Figure 3-12. The video processor decodes the bit stream data from external RAM and sends back to RAM after decoding. The decoded data is finally sent to LCD for display.